# AUTOMATING C++ EXECUTION EXPLORATION TO SOLVE THE OUT-OF-THIN-AIR PROBLEM

A THESIS SUBMITTED TO

THE UNIVERSITY OF KENT

IN THE SUBJECT OF COMPUTER SCIENCE

FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY.

Simon Cooksey May 2021

## Abstract

Modern computers are marvels of engineering. Customisable reasoning engines which can be programmed to complete complex mathematical tasks at incredible speed. Decades of engineering has taken computers from room sized machines to near invisible devices in all aspects of life. With this engineering has come more complex and ornate design, a substantial leap forward being multiprocessing. Modern processors can execute threads of program logic in parallel, coordinating shared resources like memory and device access. Parallel computation leads to significant scaling of compute power, but yields a substantial complexity cost for both processors designers and programmers.

Parallel access to shared memory requires coordination on which thread can use a particular fragment of memory at a given time. Simple mechanisms like locks and mutexes ensure only one process at a time can access memory gives an easy to use programming model, but they eschew the benefits of parallel computation. Instead, processors today have complex mechanisms to permit concurrent shared memory access. These mechanisms prevent simple programmer reasoning and require complex formal descriptions to define: memory models.

Early memory model research focused on weak memory behaviours which are observable because of hardware design; over time it has become obvious that not only hardware but compilers are capable of making new weak behaviours observable. Substantial and rapid success has been achieved formalising the behaviour of these machines: researchers refined new specifications for shared-memory concurrency and used mechanisation to automate validation of their models. As the models were refined and new behaviours of the hardware were discovered, researchers also began working with processor vendors – helping to inform design choices in new processor designs to keep the weak behaviours within some sensible bounds. Unfortunately when reasoning about shared memory accesses of highly optimised programming languages like C and C++, deep questions are still left open about how best to describe the behaviour of shared memory accesses in the presence of dependency removing compiler optimisations. Until very recently it has not been possible to properly specify the behaviours of these programs without forbidding

optimisations which are used and observable, or allowing program behaviours which are nonsense and never observable.

In this thesis I explore the development of memory models through the lens of tooling: taking at first an industrial approach, and then exploring memory models for highly optimised programming languages. I show that taming the complexity of these models with automated tools aids bug finding even where formal evaluation has not. Further, building tools creates a focus on the computational complexity of the memory model which in turn can steer development of the model towards simpler designs.

We will look at 3 case studies: the first is an industrial hardware model of NVIDIA GPUs which we extend to encompass more hardware features than before. This extension was validated using an automated testing process generating tests of finite size, and then verified against the original memory model in Coq. The second case study is an exploration of the first memory model for an optimised programming language which takes proper account of dependencies. We build a tool to automate execution of this model over a series of tests, and in the process discovered subtleties in the definitions which were unexpected – leading to refinement of the model. In the final case study, we develop a memory model that gives a direct definition for compiler preserved dependencies. This model is the first model that can be integrated with relative ease into the C/C++ programming language standard. We built this model alongside its own tooling, yielding a fast tool for giving determinations on a large number of litmus tests – a novelty for this sort of memory model. This model fits well with the existing C/C++ specifications, and we are working with the International Standards Organisation to understand how best to fit this model in the standard.

## Acknowledgements

My heartfelt thanks go to my supervisor, Professor Mark Batty, for his patience and excellent guidance during my PhD. I also thank my mother for her consistent belief in me, and my work. Thanks Mum. Finally, I write this thesis in fond memory of Jeremy Harle.

## Contents

| Abstract  Acknowledgements |      |                                    |    |  |  |

|----------------------------|------|------------------------------------|----|--|--|

|                            |      |                                    |    |  |  |

| 1                          | Intr | oduction                           | 1  |  |  |

|                            | 1.1  | Weak Memory Consistency            | 2  |  |  |

|                            |      | 1.1.1 Litmus Tests                 | 2  |  |  |

|                            | 1.2  | The Out-Of-Thin-Air Problem        | 3  |  |  |

|                            | 1.3  | Contributions                      | 6  |  |  |

|                            | 1.4  | Thesis Structure                   | 6  |  |  |

| 2                          | Me   | mory Models: State-of-the-art      | 8  |  |  |

|                            | 2.1  | Industrial models                  | 6  |  |  |

|                            |      | 2.1.1 Sequential Consistency       | S  |  |  |

|                            |      | 2.1.2 x86-TSO                      | 10 |  |  |

|                            |      | 2.1.3 ARM                          | 14 |  |  |

|                            |      | 2.1.4 C++                          | 18 |  |  |

|                            |      | 2.1.5 NVIDIA PTX                   | 21 |  |  |

|                            | 2.2  | Tools for evaluating memory models | 21 |  |  |

|                            |      | 2.2.1 Herd7                        | 21 |  |  |

|                            |      | 2.2.2 cppmem                       | 23 |  |  |

|                            |      | 2.2.3 Alloy                        | 24 |  |  |

|                            |      | 2.2.4 memalloy                     | 24 |  |  |

|                            | 2.3  | The Thin-Air Problem               | 25 |  |  |

|                            |      | 2.3.1 RC11                         | 27 |  |  |

|   |                                    | 2.3.2  | Jeffrey and Riely                                   | 28 |  |  |

|---|------------------------------------|--------|-----------------------------------------------------|----|--|--|

|   |                                    | 2.3.3  | A Promising Semantics                               | 29 |  |  |

|   |                                    | 2.3.4  | WeakestMO                                           | 31 |  |  |

| 3 | Ext                                | ending | the PTX Memory Model                                | 33 |  |  |

|   | 3.1                                | Introd | uction                                              | 34 |  |  |

|   | 3.2                                | Views  |                                                     | 34 |  |  |

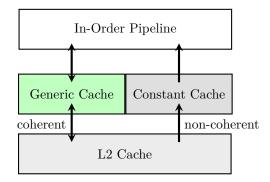

|   |                                    | 3.2.1  | Background: GPU State Spaces and Specialised Caches | 35 |  |  |

|   |                                    | 3.2.2  | Motivation: Using Specialised Processor Caches      | 37 |  |  |

|   | 3.3                                | Observ | ving mixed view behaviour                           | 37 |  |  |

|   | 3.4                                | Seque  | ntial Consistency with Constant Caches              | 39 |  |  |

|   |                                    | 3.4.1  | Baseline Formalisation of SC                        | 40 |  |  |

|   |                                    | 3.4.2  | Drawing Inspiration from TSO                        | 41 |  |  |

|   |                                    | 3.4.3  | Formalising Mixed-View SC                           | 42 |  |  |

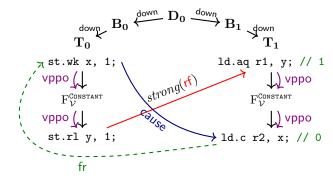

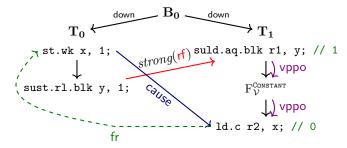

|   |                                    | 3.4.4  | Example Executions                                  | 44 |  |  |

|   | 3.5                                | Introd | uction to the PTX memory model                      | 45 |  |  |

|   |                                    | 3.5.1  | PTX Instruction Interpretation                      | 48 |  |  |

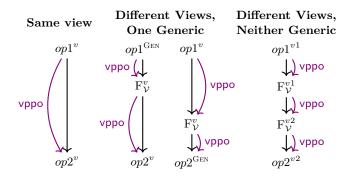

|   | 3.6                                | Views  | and Scopes in PTX                                   | 48 |  |  |

|   |                                    | 3.6.1  | Adjusting the PTX Auxiliary Relations               | 49 |  |  |

|   |                                    | 3.6.2  | Adjusting Causality                                 | 50 |  |  |

|   |                                    | 3.6.3  | Adjusting the PTX Axioms                            | 51 |  |  |

|   |                                    | 3.6.4  | Discussion: Forward Compatibility                   | 52 |  |  |

|   | 3.7                                | Valida | tion                                                | 52 |  |  |

|   |                                    | 3.7.1  | Litmus synthesis                                    | 52 |  |  |

|   |                                    | 3.7.2  | Synthesis results                                   | 55 |  |  |

|   |                                    | 3.7.3  | Model Meta-theory                                   | 60 |  |  |

|   |                                    | 3.7.4  | Theorem (Completeness)                              | 60 |  |  |

|   |                                    | 3.7.5  | Theorem (Soundness)                                 | 61 |  |  |

|   |                                    | 3.7.6  | Theorem (SC-for-DRF) $\dots$                        | 63 |  |  |

|   | 3.8                                | Conclu | ısion                                               | 64 |  |  |

| 4 | Mechanising a Thin-Air Solution 68 |        |                                                     |    |  |  |

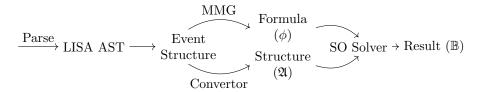

|   | 4.1                                | Archit | ecture of PrideMM                                   | 68 |  |  |

|   |                                    | 4.1.1  | Developing a memory model in SO logic               | 68 |  |  |

|   |                                    | 412    | Developing SC in SO Logic                           | 70 |  |  |

|   | 4.2  | Preliminaries                                       | 72 |

|---|------|-----------------------------------------------------|----|

|   | 4.3  | SO Solving through QBF                              | 74 |

|   | 4.4  | Memory Specification Encodings                      | 76 |

|   |      | 4.4.1 Sequential Consistency                        | 77 |

|   |      | 4.4.2 Release–Acquire                               | 79 |

|   |      | 4.4.3 C++                                           | 79 |

|   |      | 4.4.4 Jeffrey–Riely                                 | 80 |

|   | 4.5  | Evaluation                                          | 81 |

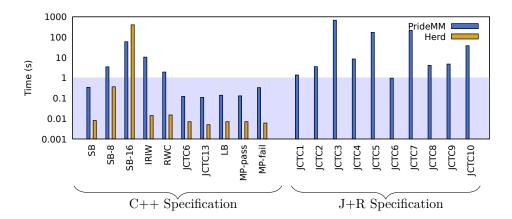

|   |      | 4.5.1 Comparison to existing techniques             | 82 |

|   |      | 4.5.2 QBF vs SO Solver Performance                  | 82 |

|   | 4.6  | Related Work                                        | 83 |

|   | 4.7  | Conclusion                                          | 84 |

| 5 | Con  | nputing Thin-Air Free Denotations                   | 85 |

|   | 5.1  | The problem with program dependencies               | 85 |

|   |      | 5.1.1 Modular Relaxed Dependency by example         | 87 |

|   | 5.2  | Event Structures                                    | 91 |

|   |      | 5.2.1 Event Structure Definitions                   | 91 |

|   | 5.3  | Coherent event structure                            | 92 |

|   | 5.4  | Memory event structures                             | 93 |

|   |      | 5.4.1 Prefixing single events                       | 94 |

|   |      | 5.4.2 Coproduct semantics                           | 96 |

|   |      | 5.4.3 Lock semantics                                | 98 |

|   |      | 5.4.4 Parallel composition                          | 98 |

|   | 5.5  | Global memory model                                 | 99 |

|   |      | 5.5.1 Language                                      | 99 |

|   |      | 5.5.2 Interpretation                                | 99 |

|   | 5.6  | Conclusion                                          | 01 |

| 6 | Fixi | ing C11                                             | 03 |

|   | 6.1  | Intermediate Memory Model (IMM) in Event structures | 03 |

|   |      | 6.1.1 Pre-execution semantic model                  | 04 |

|   | 6.2  | IMM                                                 | 10 |

|   | 6.3  | MRD+IMM                                             | 11 |

|   | 6.4  | PC11                                                | 10 |

|                           | 6.5              | MRD+RC11                                                                                                                                                         | 13        |  |  |  |

|---------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| 6.6 Comparis              |                  | Comparison with other Thin-Air Free models                                                                                                                       | 13        |  |  |  |

|                           |                  | 6.6.1 A Promising Semantics                                                                                                                                      | 14        |  |  |  |

|                           |                  | 6.6.2 WeakestMO                                                                                                                                                  | 14        |  |  |  |

|                           |                  | 6.6.3 J+R                                                                                                                                                        | 15        |  |  |  |

|                           | 6.7              | Meta-theory                                                                                                                                                      | 16        |  |  |  |

|                           |                  | 6.7.1 Overview of Proofs                                                                                                                                         | 16        |  |  |  |

|                           |                  | 6.7.2 DRF-SC                                                                                                                                                     | 17        |  |  |  |

|                           |                  | 6.7.3 Proofs in full                                                                                                                                             | 17        |  |  |  |

|                           |                  | 6.7.4 Theorem (MRD+RC11 is weaker than RC11) $\dots \dots \dots$ | 17        |  |  |  |

|                           |                  | 6.7.5 Theorem (MRD+IMM is weaker than IMM)                                                                                                                       | 19        |  |  |  |

|                           | 6.8              | Conclusion                                                                                                                                                       | 27        |  |  |  |

| _                         | ъ т              |                                                                                                                                                                  | •         |  |  |  |

| 7                         |                  |                                                                                                                                                                  | <b>28</b> |  |  |  |

|                           | 7.1              | MRDer at scale                                                                                                                                                   |           |  |  |  |

|                           | <b>7</b> 0       | 7.1.1 Related tools                                                                                                                                              |           |  |  |  |

|                           | 7.2              | Tests from the literature                                                                                                                                        |           |  |  |  |

|                           |                  | 7.2.1 Java Causality Test Cases                                                                                                                                  |           |  |  |  |

|                           |                  | 7.2.2 Common Hardware Litmus Tests                                                                                                                               |           |  |  |  |

|                           |                  | 7.2.3 Tests from other Thin-Air Free Models                                                                                                                      |           |  |  |  |

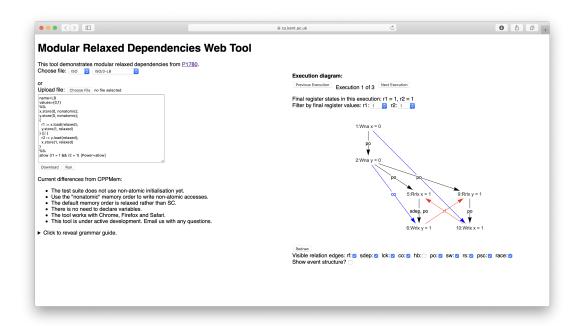

|                           | 7.3              | Web tool                                                                                                                                                         | 39        |  |  |  |

|                           | 7.4              | Conclusion                                                                                                                                                       | 39        |  |  |  |

| 8                         | Conclusion 141   |                                                                                                                                                                  |           |  |  |  |

|                           |                  | A community effort                                                                                                                                               | 42        |  |  |  |

|                           | 8.2              | Future Work                                                                                                                                                      | 42        |  |  |  |

|                           |                  | 8.2.1 C++ Standard Wording                                                                                                                                       | 42        |  |  |  |

|                           |                  | 8.2.2 Pointers in C++                                                                                                                                            | 43        |  |  |  |

|                           |                  | 8.2.3 Global Optimisations and Java                                                                                                                              | 44        |  |  |  |

|                           | 8.3              | Parting thoughts                                                                                                                                                 |           |  |  |  |

|                           |                  |                                                                                                                                                                  |           |  |  |  |

| $\mathbf{B}_{\mathbf{i}}$ | Bibliography 145 |                                                                                                                                                                  |           |  |  |  |

## Chapter 1

### Introduction

Modern computers are the result of unimaginable engineering effort over many decades. They are the among the most refined artefacts of human endeavour: the coordinated design of thousands has resulted in a construction more complex than any object built before. It is no surprise then, that aspects of how computers work are unknown even to their designers — leading to several fields of research which uncover remarkable behaviours and unintelligible bugs.

As CPU vendors have found it more and more challenging to continue an inexorable increase in clock speed, they have instead looked towards hardware parallelism to drive additional performance. This has allowed consumer CPUs to scale from machines which can execute a single instruction at a time to a complex architecture permitting dozens of concurrent threads of execution which may all access the same pool of shared memory. These multiprocessor CPUs are now commonplace in every new computer sold, and the vast majority of smartphones.

In an attempt to tame the complexity of reasoning about computer behaviour, practitioners have been developing formal abstract descriptions of processors. One such aspect which has been formally abstracted is the *memory model*: a description of what values can be returned by loads and stores. In this thesis, we will focus on so-called weak memory behaviours which arise from the complex interactions of multiprocessors sharing memory. This area of research has had significant attention over the years, particularly in the last decade – and significant strides have been made towards usable and comprehensible memory models for parallel processors.

Unfortunately, the programming languages at the core of all modern computer programs suffer even more so with weak memory behaviours than the hardware that they sit upon. Aggressive optimisations interact in unexpected ways with weakly ordered hardware, and existing approaches to formalise programming language memory models have yielded unsatisfying results.

In particular, the ISO C and C++ committee provides the authoritative definition of the C and C++ languages respectively, but their definition of memory semantics is currently incomplete (Batty et al. 2015).

#### 1.1 Weak Memory Consistency

Modern computers forgo simplicity in favour of performance. Programming languages and modern computer architectures are built with aggressive optimisations in mind, taking many forms. Compilers re-write programs making semantic preserving changes which reduce execution time – such as re-using previously computed values, or recognising that some control flow checks are unnecessary. Processor designers similarly optimise their architecture: processors might over-fetch data, or collect writes to send to system memory in blocks, amortising fixed write overheads across several operations. Unfortunately the correctness of these optimisations relies on imposing restrictions on programmers, and the assumptions that they might make about how a piece of code behaves can be wildly inaccurate. What is worse, is that many of the behaviours that result from these optimisations can only be observed occasionally if two threads sharing memory line their accesses up in time, a rare occurrence. A memory consistency model (or memory model) formally describes these behaviours, giving programmers a description of how loads and stores will behave. Memory models can be at the hardware level (i.e. x86, ARM, POWER, NVIDIA PTX) (Podkopaev, Lahav and Vafeiadis 2019; Sewell et al. 2010; Pulte et al. 2018; Sarkar et al. 2011; Lustig et al. 2017), describing how machine load and store operations work; or at the programming language level (i.e. C++, Java) (Batty et al. 2011; Manson, Pugh and Adve 2005), describing how assignments to variables behave. A memory model can be used to examine the possible behaviours of some code without having to exhaustively execute it, negating the worry that direct testing of code will not hit the sometimes one in one-billion odds of observing some architectural weakness (Alglave et al. 2011; Sewell et al. 2010).

#### 1.1.1 Litmus Tests

Added explanation of litmus tests.

An essential mechanism for understanding memory models are so-called *litmus tests*. Litmus tests are short programs designed to probe individual facets of the memory system to reveal strange behaviours. Each test comes with an expected outcome, representing the interesting behaviour. Litmus tests are normally top-level parallel with some initialisation prefixing all threads. Litmus tests are typically written in a simple grammar exposing loads, stores, conditional

control flow, and parallel composition. Additional features may be present as the memory model requires, for example, some memory models (Kang et al. 2017) support system calls, atomic read-modify-write operations (Lahav et al. 2017), and memory dereferencing (Jeffrey and Riely 2016). Throughout this thesis we will refer to litmus tests in a language extended from P below, where  ${\bf r}$  ranges over registers, M ranges over simple arithmetic expressions (including registers, but not memory locations), and  ${\bf x}$  ranges over memory locations.

$$T ::= \mathbf{r} := \mathbf{x} \mid \mathbf{x} := M \mid \mathbf{if}(\mathbf{r} = M) \{T_1\} \{T_2\} \mid T_1; T_2$$

$P ::= \mathbf{x} := 0; \dots; \mathbf{z} := 0; (T_1 \parallel T_2 \parallel \dots \parallel T_n)$

This language explicitly separates memory loads (r := x) from memory stores (x := M).

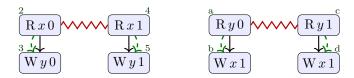

For example, Figure 1 displays the Store Buffering (SB) litmus test. SB comprises two threads which store a value to a global address, and then read a value from a different address. It demonstrates a weak behaviour admitted by an architectural feature of x86 where the weak behaviour  $\mathbf{r}_1 = \mathbf{r}_2 = 0$  can be observed. A naïve programmer might not expect this execution, because no interleaving of the operations of threads 1 and 2 would yield a state where both the reads can read from the initialisation of x and y. In practice this execution is allowed because of behaviours introduced by optimisations in the x86 architecture, the exact mechanism for which is explained in §2.1.2. In fact a compiler optimisation can also introduce this behaviour: a compiler can observe that the write to x is unrelated to the subsequent read from y, and re-order the accesses.

Initially:

$$x := 0$$

;  $y := 0$ ;

$x := 1$ ;  $y := 1$ ;

$r_1 := y$   $r_2 := x$

Figure 1: Store buffering litmus test. The weak behaviour would be observing that  $r_1 = r_2 = 0$ .

The common patterns of litmus tests are those which show certain kinds of multi-thread synchronisation. A popular set of these tests comes from the supplemental material with the POWER memory model (Maranget, Sarkar and Sewell 2012). It lists the most common synchronisation patterns and where a weak behaviour is permitted, and annotates each example with what additional POWER instructions must be added to forbid the weak behaviour.

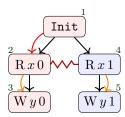

Figure 2: Load buffering litmus test (LB).

Initially:

$$x := 0$$

;  $y := 0$ ;

$r_1 := y$ ;

$if(r_1 = 1) \{x := 1\}$   $r_2 := x$ ;

$if(r_2 = 1) \{y := 1\}$

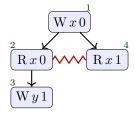

Figure 3: Load buffering litmus test, with data dependencies (LB+deps).

#### 1.2 The Out-Of-Thin-Air Problem

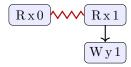

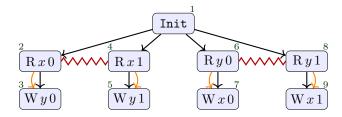

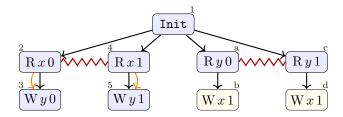

The current formal definitions of Java (Manson, Pugh and Adve 2005) and C/C++ (ISO/IEC 2010) allow program executions which appear to summon values *Out of Thin Air* (OOTA) (Pugh 1999; Batty et al. 2015). To explore OOTA executions, we will consider a handful of programs and how they might execute. Figure 2 presents the Load Buffering (LB) litmus test which is a canonical reference for exploring OOTA (Batty et al. 2015; Kang et al. 2017; Pichon-Pharabod and Sewell 2016; Jeffrey and Riely 2016; Paviotti et al. 2020). LB is a two thread litmus test in which each thread reads from a shared location and then writes to a different shared location.

In this case, we might wonder if we can observe the weak behaviour where  $\mathbf{r}_1 = \mathbf{r}_2 = 1$ . Either because of architectural features that allow re-ordering of the apparently unrelated loads and stores of each thread, or compiler optimisations which do the same. Indeed, as some hardware does this re-ordering (Maranget, Sarkar and Sewell 2012; Deacon and Alglave 2019) it is necessary to forbid the weak behaviour. Fences incur a performance penalty, so doing so is undesirable, and indeed C/C++ compilers do not emit them: allowing the weak behaviour. All other outcomes of LB could be explained by executing the program one instruction at a time without re-ordering.

Let's consider a modification of this program, which should prevent the weak execution. In Figure 3 we have introduced a condition on each thread, contingent on the value read in the operation before the store. In this case a compiler could not re-order the operations, as they now are related.

So the memory model must allow the weak execution in the first program, LB, but forbid the weak execution of the second program, LB+deps. Informally this execution must be forbidden because calculation of non-zero values in r1 and r2 is self-referential: one must first read the

```

Initially: x := 0; y := 0;

r_1 := y; 	 r_2 := x;

if(r_1 = 1) \{ 	 if(r_2 = 1) \{ 	 y := 1 \}

else \{ 	 y := 1 \}

f(r_2 = 1) \{ 	 y := 1 \}

```

Figure 4: Load buffering litmus test, with false data dependencies (LB+false-dep).

Initially:

$$x := 0$$

;  $y := 0$ ;

$r_1 := y$ ;  $r_2 := x$ ;

$x := r_1$   $y := r_2$

Figure 5: Load buffering litmus test, with data dependencies (LB+datas). The OOTA behaviour would be observing that  $r_1 = r_2 = 42$ .

value, to write it, and to read it the other thread must have written it – so must have read the value... and so on. Naïvely we might try and capture this kind of cycle in value calculation. To explore this idea a little further, let us consider another program, LB+false-deps, printed in Figure 4.

In LB+false-deps a compiler can trivially optimise the program back to the original LB (Figure 2) as regardless of the control flow choice, the assignment of  $\mathbf{x} := 1$  will happen regardless. As a result, the memory model must allow the outcome  $\mathbf{r}_1 = \mathbf{r}_2 = 1$ . Thus simply observing in a single execution that there's some cyclic calculation of the value for  $\mathbf{r}_1$  and  $\mathbf{r}_2$  does not imply the execution should be forbidden. Things get worse, though. Consider the program in Figure 5: it would be peculiar for  $\mathbf{r}_1 = \mathbf{r}_2 = 42$ : the value 42 does not appear in the code, and cannot be calculated from the values in the program. Yet, the C/C++ memory model allows the execution for the same reason it allowed  $\mathbf{r}_1 = \mathbf{r}_2 = 1$  for LB+false-deps.

Unfortunately this is because the C/C++ memory model cannot detect which dependencies are merely *syntactic*, i.e. dependencies which can be eliminated by compiler optimisation, and which dependencies are are *semantic* (McKenney et al. 2016), i.e. dependencies which materially affect the execution of the program. This inability to distinguish LB and LB+datas is known as the *Out-Of-Thin-Air Problem*, and is the focus of much of the content of this thesis. OOTA is a big problem: consider that the data stored in x of LB+deps is actually a pointer which should only be handed over when a certain security constraint is met, perhaps it points to some secret

data. Having a memory model which allows thin-air executions means that we cannot prove that our LB program does not gain access to the secret memory – even though in reality it could not execute like that with any combination of hardware and compiler. This ability to summon illegal pointers is a barrier to proving safety properties like no use-after-free, or some kinds of buffer over runs.

#### 1.3 Contributions

This work is a step towards a new standardised version of the C/C++ memory model which permits aggressive compiler optimisations and forbids thin-air executions. This thesis makes the argument that tools are essential to building and understanding complex memory model. Ultimately a tools based approach has allowed us to define a new memory model for C/C++ which shows a lot of promise (Giroux 2019).

Understanding concurrency in C/C++ is something that has driven significant research effort over several years (Kang et al. 2017; Pichon-Pharabod and Sewell 2016; Jeffrey and Riely 2016; Chakraborty and Vafeiadis 2019), and part of what makes it so complex is that a *good* definition for the C/C++ memory model must be sensitive to two things. First, it must be a mathematically sound and usable way to prove useful properties about concurrent programs. Secondly, it must fit with the existing C/C++ standard without widespread rewrites to substantial portions of the standard text. The C/C++ standard is a contract between language implementers and programmers, so re-writing large sections of that is not a noble thing nor remotely likely to be approved. While reasoning about thin-air free memory models, we find that tools to execute these models are the ultimate mechanism to detect bugs and explain the model to others.

Progress towards this goal took place in stages, first looking at axiomatic models for hardware execution, then examining thin-air models, before finally proposing a solution of our own. Concretely, the thesis contributions are as follows:

- A better understanding of memory system features in NVIDIA PTX

- The first tool to automatically evaluate a thin-air free memory model over a suite of litmus tests

- A denotational model of weak memory consistency which provides a definition of semantic dependency

- Integration of semantic dependency into a full-fat C/C++ memory model to provide a thin-air free C/C++ memory model

#### 1.4 Thesis Structure

In this thesis we will see why tools are essential for tackling the complexity of building and reasoning about weak memory consistency models. This thesis contains 3 case studies, each using tools to aid building concurrency models. These case studies work from the ground up, starting at hardware and working towards a sensible model of C/C++ which permits optimisations, but does not allow thin-air free executions.

**NVIDA PTX** In the first case study, Chapter 3, we look at the NVIDIA PTX memory model which is the hardware model for NVIDIA graphics cards. We extend PTX to cover more hardware features, and introduce new relaxations. Tools are used to validate that these changes do not interfere with the previous definition, and to generate exhaustively programs which might execute in a weakly consistent manor on the hardware.

An Event Structures Model of Relaxed Memory. In the second case study, Chapter 4, we look at the thin-air free model for Java presented by Jeffrey and Riely (2016). They present a formula for exploring the possible states of a program execution, yielding a novel thin-air free semantics for Java. In this instance we develop a tool to automatically evaluate the model over a suite of litmus tests. This process uncovered a bug with their model, and led to a fix – even despite existing mechanised proofs.

Modular Relaxed Dependencies. In the final case study we develop a thin-air free C++ semantics which covers much of the C++ language and forms a candidate to drop into the existing C++ specification. Modular Relaxed Dependencies (MRD), defined in Chapter 5 solve the thin-air problem by decoupling the calculation of dependencies which are semantic from the syntax of the program. We then use this semantic dependency calculation to build a fully featured C/C++ model, Chapter 6, the existing axiomatic model provided by (Lahav et al. 2017) and re-expressed by (Podkopaev, Lahav and Vafeiadis 2019). The construction of MRD has a blended approach of execution exploration and per-execution axiomatic restriction, the development of which was strongly informed by the concurrent building of a tool for automatic evaluation over many litmus tests. Thus, in Chapter 7, we analyse the semantics in the context of other thin-air free models, using automatic evaluation to mechanically derive permitted executions for a suite of litmus tests in the literature. This was presented as a paper at ESOP 2020 and has formed a working paper for the ISO C++ Standards Committee.

## Chapter 2

## Memory Models: State-of-the-art

Memory model development has seen substantial academic interest over the past decade. A focus on formal specification and empirical model validation have resulted in large strides forward for reasoning about software behaviour. In this chapter we will introduce memory model concepts and tour the key academic developments in memory model formalisation over the last few years. We will start with a model for a simple concurrent machine, and subsequently introduce more modern and weakly ordered hardware. Once we have considered hardware we will move on to look at programming language models, the Out-Of-Thin-Air (OOTA) problem, and some existing solutions to OOTA.

Programmers need to understand how their code will execute on real hardware in order to write bug-free software. To talk about memory models concretely, we will first pin down a couple of definitions. *Memory models* are precise specifications of what values can be returned by loads. *Consistent* executions of a program are those which are allowed by the memory model, i.e. all the loads returned in the execution satisfy the constraints of the memory model. These consistent executions provide bounds on program behaviour, but a given allowed execution may not be observable in practice. A memory model's *strength* describes how many executions are permitted for a given program, and comparing memory models can be done with quantitative comparisons of their strength. The stronger a memory model, the fewer executions it allows, the weaker a model, the more executions it allows. Programming language designers and processor architects design their systems with particular programming idioms and optimisations in mind. The strongest possible memory model would permit no executions of any programs, while the weakest would allow any execution of any program. These extremes of strength and weakness are not useful, so memory models of interest sit in the spectrum in-between. Stronger memory

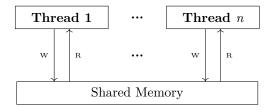

Figure 6: SC block diagram

models typically allow more use of more straightforward programming idioms, whereas weaker models allow more aggressive optimisation of code. In this literature review we will explore important memory models for concurrency, from the strongest model of Sequential Consistency (§2.1.1) to the weakest models of ARM (§2.1.3) and C++ (§2.1.4).

#### 2.1 Industrial models

#### 2.1.1 Sequential Consistency

A simple model of memory behaviour in a concurrent setting is the model of Sequential Consistency (SC). This model, described by Lamport (1979), presents a simple "interleaving semantics" of memory accesses, where each thread in the system takes one step at a time modifying a single global shared memory. Lamport concisely describes a machine as sequentially consistent if:

... the result of any execution is the same as if the operations of all processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.

- Lamport (1979)

A simple block diagram of an SC machine is shown in Figure 6. The SC machine has n threads, each with arrows to indicate their data paths for reads (R) and writes (W) to a single shared memory. Each thread can read or write the shared memory one at a time, which creates the interleaving. As such, there is a single global order of stores to memory which is the same to all observers. Let's consider SB again (Figure 7), and all of the possible SC executions of that program: i.e. all of the sequential orders that the operations could be performed in Lamport (1979).

Initially:

$$x = y = 0$$

Thread 1 Thread 2

$$x := 1;$$

$y := 1;$   $r_1 := y$   $r_2 := x$

The interleaved programs can be displayed conveniently as a single stream of operations which are executed left to right. There are six valid interleavings: two simple cases where Thread 1 fully executes, then Thread 2 and vice versa; and 4 other executions where operations alternate between the two threads. The first case where Thread 1 fully executes then Thread 2 would be represented as x := 1;  $r_1 := y$ ; y := 1;  $r_2 := x$  – where 1 is written to x, 0 is read from y, 1 is written to y and finally 1 is read from x. This yields an execution where we observe  $r_1 = 0 \land r_2 = 1$ . Each execution and the final state of the registers is enumerated in the table below.

|                                      | Final State |                |

|--------------------------------------|-------------|----------------|

| Sequentialised code                  | $r_1$       | $\mathtt{r}_2$ |

| $x := 1; r_1 := y; y := 1; r_2 := x$ | 0           | 1              |

| $y := 1; r_2 := x; x := 1; r_1 := y$ | 1           | 0              |

| $x := 1; y := 1; r_1 := y; r_2 := x$ | 1           | 1              |

| $y := 1; x := 1; r_1 := y; r_2 := x$ | 1           | 1              |

| $x := 1; y := 1; r_2 := y; r_1 := x$ | 1           | 1              |

| $y := 1; x := 1; r_2 := y; r_1 := x$ | 1           | 1              |

Under sequential consistency the final state  $\mathbf{r}_1 = 0 \wedge \mathbf{r}_2 = 0$  is not observable, which matches the naive assumption that loads and stores can't be reordered. Unfortunately for programmers SC behaviour is not something one can take for granted, and real computer systems are more complex. As far back as 1972 with the IBM System 370/158MP (Maranget, Sarkar and Sewell 2012), processors have exhibited non-sequentially consistent behaviour: where program executions do not correspond to an interleaving of each thread's instructions. Further, key architectures available today (ARM, x86, POWER, RISC-V...) are also more weakly consistent. To understand this better, let us first examine x86.

#### $2.1.2 \times 86-TSO$

There is an inherent tension between hardware architects and software engineers: hardware architects want to specify the weakest possible architecture, to permit more aggressive optimisation

in the future, while software engineers need to write well specified programs which are built on guarantees provided by the underlying hardware.

When trying to understand the precise behaviour of memory accesses on x86, Sewell et al. (2010) found contemporary specifications from hardware vendors to "leave key questions ambiguous". To better understand how weak memory in x86 can affect concurrent programs it is possible to construct small programs whose behaviours are non-SC. Where study of the specifications reveals ambiguity, tests can be carefully crafted to help answer the questions raised. Observation of a weak behaviour on hardware is enough to evidence a weak behaviour is possible, and not being able to observe a behaviour allows researchers to ask questions of hardware architects about specific assumptions of the architecture's design. It is not a guarantee that not observing a weak behaviour means that the architecture will always forbid it, either. Architects may implement optimisations which result in new observable weak memory behaviours without changing the specification of their machines.

#### Weak behaviours and Litmus Tests

To explore x86 we begin as Sewell et al. (2010) did and investigate some short programs – known as *litmus tests* – which shed light on the weak behaviours.

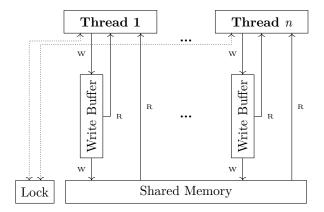

Store Buffering. Store Buffering (SB) is shown in Figure 7, and is a key example that demonstrates a non-SC behaviour on the x86 architecture – it is the same example we examined under Sequential Consistency (§2.1.1), but instead presented in concrete x86 assembly. Figure 8 gives a high-level block diagram for memory accesses in x86: arrows indicate dataflow between hardware threads and memory. The write buffer is a cache for stores to memory and is the implementation of an architectural optimisation which reduces the latency of local accesses to a memory location and reduces bandwidth requirements to shared memory. This optimisation introduces a new weak behaviour: the execution of interest in Figure 7 is one where EAX ==  $0 \land EBX == 0$ , and does not correspond to an SC execution of the program – there is no interleaving of operations which would leave the register file in this state.

Each hardware thread's write buffer is a read/write cache which can "short-circuit" accesses to shared memory when there has been a recent store to a given location in the same thread. Considering each thread in turn: Thread 1 first stores value 1 into x, which is cached in a write buffer; Thread 2 similarly stores 1 in y – and is also cached in the local write buffer. Then each thread performs a load, Thread 1 does not have a value for y in its local write buffer, so reads the now-stale value 0 from shared memory. Similarly, Thread 2 does not have a value for x in its

```

Initially: \mathbf{x} = \mathbf{y} = 0

Thread 1

MOV [x], 1;

MOV EAX, [y];

MOV EBX, [x];

```

Figure 7: Store buffering in x86 assembly. Observing  $EAX == 0 \land EBX == 0$  after this program executes corresponds to a weak memory behaviour.<sup>1</sup>

Figure 8: x86-TSO block diagram

write buffer and also reads a stale value of 0 from shared memory.

Message Passing. Message Passing (MP), shown in Figure 9, reflects a common notify-wait programming pattern. A producer thread does some computation to calculate a value to store into  $\mathbf{x}$ , and then notifies a waiting thread that the value is ready by setting a flag in  $\mathbf{y}$ . The write buffer propagates values to shared memory in order, meaning that the write of the flag cannot "overtake" the write of the data. As such,  $\mathtt{EAX} == 1 \land \mathtt{EBX} == 0$  is forbidden. This test shows that local store-store ordering is respected globally. As we will see later in §2.1.3 other architectures are weaker and require additional operations to preserve ordering between stores. This makes MP a useful test to contrast the behaviours present in x86 with, for example, ARM.

<sup>&</sup>lt;sup>1</sup>Registers are local to each thread, but it is clearer to use unique register names to disambiguate final states.

| Initially:  | x = y = 0 |      |

|-------------|-----------|------|

| Thread 1    | Thread 2  | ļ    |

| MOV [x], 1; | MOV EAX,  | [y]; |

| MOV [y], 1; | MOV EBX,  | [x]; |

Figure 9: Message passing in x86 assembly. Observing  $\mathtt{EAX} == 1 \land \mathtt{EBX} == 0$  after this program must be forbidden.

```

Initially: x = y = 0

Thread 1

MOV [x], 1;

MFENCE;

MOV EAX, [y];

MFENCE;

MOV EBX, [x];

```

Figure 10: Store buffering in x86 assembly with MFENCE instructions. Observing EAX ==  $0 \land \text{EBX} == 0$  is now forbidden.

#### **Restoring Order**

It is of course undesirable to always have weak memory effects, as they can break fundamental building blocks of shared memory communication, such as Store Buffering (Figure 7). As such, in x86 there are operations available which prevent the store buffers from apparently re-ordering stores. x86 provides an instruction which flushes the store buffers to system memory, providing the following guarantee:

[MFENCE p]erforms a serializing operation on all load-from-memory and storeto-memory instructions that were issued prior the MFENCE instruction. This serializing operation guarantees that every load and store instruction that precedes the MFENCE instruction in program order becomes globally visible before any load or store instruction that follows the MFENCE instruction.

— Intel 64 and IA-32 Architectures Software Developer's Manual (Intel Corporation 2016)

Thus in x86 inserting MFENCE instructions on each thread of the original store buffering program will forbid the weak execution. We will call this new program SB+fences, and it is printed in Figure 10. By serialising the loads-from-memory and the stores-to-memory we can ensure there is a simple interleaving, and we restore sequentially consistent behaviour. That is, with MFENCE we will forbid the outcome EAX ==  $0 \land EBX == 0$ .

Validation. A formal model of x86 is useful only if it can be trusted as a faithful model of software running on the platform, and without vendor endorsement the only way to build trust is exhaustive execution of tests. Alglave et al. (2011) provide a tool, litmus, for running litmus tests against hardware. litmus takes care to use fine control of thread start and processor state to give hardware the best chance to exhibit rare weak memory behaviours.

Using litmus does build substantial confidence that the model is accurate – discrepancies would be obvious, but litmus does not show a model to be *complete*: it cannot provide a guarantee that all weak behaviours are covered. Nor can litmus show a model to be *sound*: it

Initially:

$$x = y = 0$$

Thread 1 Thread 2

$x := 1;$   $x_1 := y;$   $x_2 := x$

Figure 11: Pseudocode Message Passing litmus test. Observing  $\mathbf{r}_1 = 1 \wedge \mathbf{r}_2 = 0$  is permitted on ARM.

cannot provide a guarantee that all weak behaviours permitted by the model can be observed on the hardware. litmus is an empirical tool, and as Sewell et al. (2010) note: "there may be tests where x86-TSO allows some final state that cannot be observed in practice". Despite this, litmus provides a useful lens into processor behaviour – allowing the execution of manually selected interesting tests, and as we will see later in section §2.2.1, the execution of tests automatically generated from formal specifications of memory models.

#### 2.1.3 ARM

ARM designs a family of architectural specifications which are implemented by vendors like Broadcom, Qualcomm, and Apple. Some of these designs are small-scale single-threaded embedded platforms, but others are large application processors which run in consumer electronics, mobile phones, and servers. These larger processors support multiprocessing, and exhibit a weaker memory model than x86. The ARM memory model is provided in ARM's architecture manual as an english language specification (ARM 2020, 2014), and a formal mathematical definition in the form of a CAT model (Deacon and Alglave 2019; Alglave, Maranget and Tautschnig 2014). CAT models will be explored in greater detail in §2.2.1.

To see how ARM is weaker than x86, we can look at MP again. This time MP is presented in Figure 11. Unlike the previous presentation of MP, the litmus test now is rendered in psuedocode. ARM is a RISC architecture which requires more instructions to express programs, so the psuedocode treatment keeps presentation clear.

In MP on x86, executions where  $\mathbf{r}_1 = 1 \wedge \mathbf{r}_2 = 0$  are forbidden, as loads from a single thread of execution cannot appear to be executed out-of-order. On ARM however, this behaviour is observable. Threads can "snoop" values from other threads' local caches without being compelled to observe all of the stores available in that cache. This allows stores to appear to "overtake" one another in the memory system – where a snoop into an adjacent cache can return faster load from main memory, allowing the weak execution of the MP litmus test.

To better explain executions and weak behaviours in memory consistency models it is useful

Initially:

$$x = 0$$

Thread 1 Thread 2

$x := 1;$   $r_1 := x;$

$x := 2$   $r_2 := x$

Figure 12: Pseudocode CoRR litmus test. Observing  $\mathbf{r}_1 = 2 \land \mathbf{r}_2 = 1$  is forbidden on ARM.

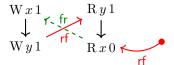

to draw executions graphically. First, let's examine the SC execution where  $r_1 = 1 \land r_2 = 1$ .

$$\bigvee_{\text{W }y \, 1}^{\text{W }x \, 1} \bigvee_{\text{rf}}^{\text{R }y \, 1}$$

We will begin to use a style of drawing executions that is common in the literature (Batty et al. 2011; Lahav et al. 2017; Alglave, Maranget and Tautschnig 2014). Nodes indicate whether a value is read or written to memory, the location of the operation, and the value loaded/stored. For example,  $R \times 0$  indicates the value 0 is loaded from x, and W y 1 indicates that 1 is stored to y. Black arrows indicate program order (po), i.e. the order that the operations occur syntactically in the program. Red arrows indicate where a load read its value from, with the reads from (rf) relation.

Figure 12 shows an example to understand coherence order (co): the Coherence-ordered Read Read (CoRR) test shows us that for two reads in a row - observing the write of 2 hides the initialisation write. Coherence order is a total order<sup>2</sup> per-location, giving a "store order" to each variable.

The forbidden execution of CoRR is drawn below:

$$\begin{array}{c} W x 1 \\ co \downarrow \downarrow \\ W x 2 \end{array} \xrightarrow{\mathsf{rf}} \begin{array}{c} R x 2 \\ R x 1 \end{array}$$

To understand why this execution is forbidden in the ARM memory model, we must look at a relation which can be calculated from rf and co. From-reads (fr) places reads to a given location into an order with respect to coherence order.

$$fr \triangleq rf^{-1}$$

: co

<sup>&</sup>lt;sup>2</sup>co is a total order in multicopy-atomic (MCA) systems, as opposed to non-multicopy-atomic (non-MCA) systems where it is a partial order. Earlier revisions of the ARM ISA allowed non-MCA stores, but this has been revised and ARM is now MCA (Pulte et al. 2018).

Where  $[-]^{-1}$  inverts a relation (reverses all the arrows), and ; composes relations (links arrows together). We can annotate the CoRR execution with an fr edge to demonstrate this. Here we can compose rf and co such that  $(Rx1 \xrightarrow{rf^{-1}} Wx1 \xrightarrow{co} Wx2)$  forms an fr edge. Another derived relation is program order per location (po\_loc) which is the subset of program order relating events on the same memory address. In this program with only one address all the po edges are also po\_loc. The execution is drawn again below including the fr edge, and one of the po\_loc edges highlighted.

$$\begin{array}{c} W x 1 \\ co \swarrow \\ W x 2 \leftarrow \begin{matrix} rf \\ -rf \\ -rf \end{matrix} & \downarrow \\ po\_loc \\ R x 1 \end{array}$$

An axiom included in the ARM memory model forbids cycles in  $po\_loc \cup fr \cup rf \cup co$ , making this execution forbidden as there the cycle (R x 2  $\xrightarrow{po\_loc}$  R x 1  $\xrightarrow{fr}$  W x 2  $\xrightarrow{rf}$  R x 2) is present (ARM 2020; Deacon and Alglave 2019).

Now, recall MP (Figure 11) and consider the non-SC execution where  $r_1 = 1 \land r_2 = 0$ .

In this weak execution of MP, the read of x as 0 can be seen to come before the write of 1 to x. The rf edge drawn from a red dot it indicates the load reads from the initialisation. The implicit initialisation event is co-before all writes, which is what gives us the fr edge:  $(R x 0 \xrightarrow{rf^{-1}})$  (initialisation)  $\xrightarrow{co} W x 1$ ). Although this execution is similar in shape to CoRR, the absence of po\_loc makes all the difference. The axiom which forbids the apparent reordering of reads to the same location does not apply here, the cycle is broken as there is no po\_loc edge. Under x86 this execution is forbidden, writes cannot appear to overtake one another, similarly for reads. A key insight about ARM, then, is that the apparent re-ordering of loads or stores is observable, so long as they are not loads and stores to the same location.

Message passing is a useful communication primitive in software systems, so it is desirable to restore sequentially consistent behaviour. To do this, the ARM architecture provides barriers which prevent hardware re-ordering of loads and stores. The DMB (known as the Data Memory Barrier) instruction prevents instructions appearing to be executed out-of-order.

Data Memory Barrier acts as a memory barrier. It ensures that all explicit memory accesses that appear in program order before the DMB instruction are observed before any explicit memory accesses that appear in program order after the DMB instruction. It does not affect the ordering of any other instructions executing on the processor.

Thus, to prevent the reordering of loads and stores and hence prevent weak execution of MP: a DMB instruction must be placed in each thread, as shown below.

Initially:

$$x = y = 0$$

Thread 1 Thread 2

$x := 1;$   $r_1 := y;$

DMB; DMB;

$y := 1$   $r_2 := x$

Instructions separated by a DMB instruction are related by the *Barrier Ordered Before* (bob) relation in the corresponding executions (ARM 2020; Deacon and Alglave 2019), the weak execution of MP is drawn below, with the bob annotations.

$$\begin{array}{c} W x 1 \\ bob \bigvee \\ W y 1 \end{array}$$

The ARM models forbids cycles in ( $\mathsf{rf} \cup \mathsf{fr} \cup \mathsf{bob}$ ) so this execution is forbidden (Deacon and Alglave 2019; ARM 2020).

**ISA2.** An important concept in the ARM memory model is the cumulativity of synchronisation. When passing a message through multiple threads of execution it is important that synchronisation can be propagated. This concept demonstrated concisely with the ISA2 litmus test.

Observing  $\mathbf{r}_1 = 1 \wedge \mathbf{r}_2 = 1 \wedge \mathbf{r}_3 = 0$  indicates that despite a flag (y and z) being propagated between the 3 threads the data (x) is not. This execution is permitted on ARM. The hardware will not enforce the order of the loads or stores.

To rectify this, ordering must be enforced. For thread 1, the same DMB instruction can be issued to ensure ordering between the store of x and y. For threads 2 and 3, load-store ordering can be enforced using address dependencies. An operation A is address-dependent on an operation B when the value returned by operation B is required to compute the address used in operation A. A modified ISA2 with DMB and address dependencies is displayed below.

The pointer arithmetic in the modified ISA2 has no effect on ultimate addresses, but it forces the hardware to preserve ordering between the load and store in thread 2, and the loads in thread 3. The address dependencies are represented by the addr relation. When we consider the weak execution of our modified ISA2 we find a cycle in  $(bob \cup addr \cup fr)$ , which is also forbidden in the ARM memory model.

#### 2.1.4 C++

The C and C++ Programming languages are critical low-level systems languages used in the majority of computer software. Windows is written in C++; Linux, BSD, and macOS are written in C (Torvalds 2021; Group 1983; Apple Inc. 2021); web browsers like Firefox and Google Chrome are written in C++ (Mozilla Project 2021; Project 2021). With C and C++ forming the foundations of critical computer software it is important that the languages are well understood and can be formally modelled. In the past the C and C++ standards were written carefully in English language prose, but had no formal mathematics behind them.

Figure 13: Two litmus tests in abbreviated C++ syntax. Relaxed message passing (MP) is on the left and release/acquire message passing (MP+rel+acq) is on the right. In both programs x = y = 0 initially.

A requirement of the C and C++ programming language is that they give programmers direct access to the high performance code paths available in modern CPUs, like relaxed atomics and high performance vector instructions. In order to support this, the language memory model must permit the weak behaviours observable in the hardware, so the C and C++ memory models are weaker than their hardware counterparts (like x86-TSO and the ARM memory model). Were the C++ model to provide stronger guarantees it would mean that compilation of certain patterns of loads and stores would incur additional fences. For example, if C++ were designed to be as strong as x86-TSO the C++ ARM compiler would need to insert DMB barriers between each store instruction to prevent the weak MP behaviours observable on ARM hardware.

Happens before. With Mathematizing C++ (Batty et al. 2011) introduced a formal mathematical model of C++ which has been iterated upon and incorporated into the C++ standards text (ISO/IEC 2010). Since the adoption of the Mathematizing approach in the 2011 C++ standard, revisions have been made: most notably revisions proposed by Lahav et al. (2017) (known as RC11), which fixes the treatment of SC atomics in C++ have been adopted, but the RC11 approach to forbidding thin-air executions has not – this will be discussed in more detail in Section 2.3.1. The model is defined in terms of a "happens before" relation (hb), where cycles are forbidden. To explore this model, we will again look at a message passing (MP) litmus test. Figure 13 shows two versions of MP with different annotations to denote access mode. Access modes result in the compiler, one with a release/acquire pair and one with all relaxed accesses. The same  $\mathbf{r}_1 = 1 \wedge \mathbf{r}_2 = 0$  outcome is drawn for each, but in the release acquire version the hb edges form a cycle, so the execution is forbidden by the C++ memory model. In the relaxed variant of MP we see that all the program order edges are in hb order, but the rf edge

is not. Accesses which appear in happens before order are synchronised, and the hb order of these actions can be relied upon in other threads of execution. In this way, we build lock-free racy programs with defined semantics – observable values are restricted by the actions available hb-before a given read.

To understand why, we can look at the definition of happens before, a subset of which is presented below.

$$\mathsf{hb} \subseteq ([E^{\sqsubseteq rel}]; \mathsf{rf}; [E^{\sqsubseteq acq}]) \cup \mathsf{po}$$

We can see that happens before contains all of program order (po) as well as rf edges which go between events of at least release strength to events of at least acquire strength. In both of the examples in Figure 13 we can see that the po edges coincide with an hb edge. In our relaxed program the rf edge between the load and the store are both relaxed, so the rf edge is not included in hb. Conversely in the release/acquire variant the rf edge goes between a store with acquire strength to a load with release strength, making the rf edge part of hb.

Another edge visible on these diagrams is the from-reads (fr) edge, also known as "reads before". fr indicates that a read observes some value which was written before some other write to the same location. In these weak MP executions the reads on x both read from the initialisation, which are coherence ordered before the store of x := 1. Along with rf and co, fr is among a category of relations which order operations on the same location. These relations are collected into one definition called extended coherence order (eco).

$$eco \triangleq (rf \cup co \cup fr)^+$$

C and C++ have a coherence axiom which states that hb; eco? must be irreflexive, preventing cycles in calculation of a value at one location.

This axiom forbids the weak execution of release/acquire MP – there is a cycle of hb; hb; eco –but permits the weak execution of relaxed MP as the rf arrow is not part of hb, breaking the cycle.

Races and Catch-fire semantics. Data-races are a programming hazard in C and C++, but building racy code can be useful in some circumstances. For example, when building a fast scheduler it is not critical that a task is selected from a queue deterministically. However, it is useful to be able to optimise code assuming that no code is racy, it allows reordering of

loads and stores which in practice yields significant execution speed-up. To allow these opposed pressures to coexist in C and C++ the standard has two flavours of non-synchronising memory access: non-atomic and relaxed. Races between relaxed accesses have defined semantics, such as that of the weak execution of relaxed MP shown on left in Figure 13 – these races appear in hb-order. Races between non-atomic accesses however exhibit undefined behaviour (UB): the whole program may do anything when code with UB is executed, including simply exiting with a 0 return code. For this reason, the C and C++ concurrency is known as a catch-fire semantics, where hitting UB means the program can have any execution at all, including totally nonsensical ones – colloquially the machine halting and catching fire is a valid execution for a racy program.

#### 2.1.5 NVIDIA PTX

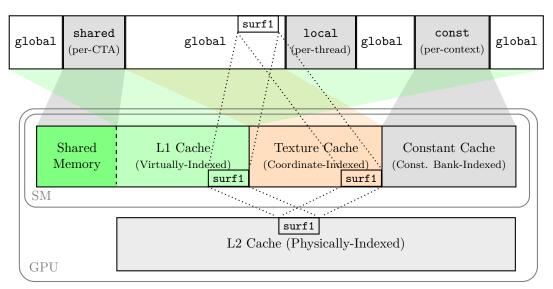

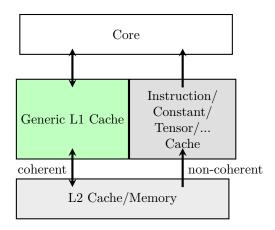

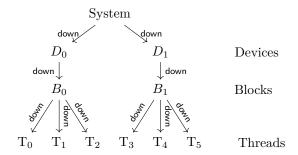

Modern graphics cards are have many thousands of threads accessing the same pool of shared memory, and the organisation of these threads is in part determined by the programmer and in part determined by the hardware.

NVIDIA provide a virtual instruction set for their graphics cards (Lustig et al. 2017). This instruction set acts as an intermediate between the assembly language for a given hardware generation and compilers, allowing for flexibility of implementers to change the instruction set between generations.

The PTX memory model is quite complex, as not only does it have an acyclicity relation along the lines of C++'s hb, but it is also *non-multicopy atomic* – meaning that two threads may observe stores to a single location in contradictory orders. The hardware gives programmers the facility to restore multicopy atomicity using special annotations, but those annotations require careful reflection of the program execution structure on the hardware.

### 2.2 Tools for evaluating memory models

As memory models are complex, and interactions between definitions are hard to exactly characterise there has been work on making automated tools for evaluating litmus tests under a given memory model. The most successful such tool is Herd7 (Alglave, Maranget and Tautschnig 2014), which provides a syntax for specifying axiomatic memory models as well as accepting tests generated by the LISA tool in LISA syntax. Other tools have been made to automatically compare memory models to discover litmus tests which tell them apart (Wickerson et al. 2017). Further tools can run litmus tests on hardware and characterise their behaviours. These tools have been important to discover previously undocumented hardware behaviours, particularly

```

include "fences.cat"

include "cos.cat"

(* Atomic *)

empty rmw & (fre;coe) as atom

(* Sequential consistency *)

show sm\id as si

acyclic po | ((fr | rf | co);sm) as sc

```

Figure 14: CAT specification of a sequential consistency memory model

where hardware implementers have been reticent to work with academics.

#### 2.2.1 Herd7

SC

Herd7 (Alglave, Maranget and Tautschnig 2014) is a tool which allows memory model designers to express axiomatic memory models in a customisable language and to then automatically validate litmus test outcomes. It works in the diy suite of tools which provide a full suite of programs for litmus test synthesis, execution on real hardware, and mechanical means to determine which outcomes are permitted for a given litmus test according to a given memory model.

Herd provides a simple language for expressing memory models called the CAT language which has been formally specified by Alglave, Cousot and Maranget (2016). The language provides primitives for developing axiomatic memory models conforming to a broadly applicable interface. For example, (Alglave, Maranget and Tautschnig 2014) provides an example of a model of sequential consistency, printed in Figure 14.

This model defines two axioms which must hold for an SC execution of a program. The first is empty rmw & (fre;coe) as atom which specifies that the intersection of rmw and  $fr_e$ ;  $co_e$  is empty. Digesting that definition a little: it prevents execution fragments of the shape presented in Figure 15. In this execution fragment we can see a write apparently happening in the middle of an atomic read-modify-write operation. This "splitting the atomic" behaviour is forbidden by atomicity axiom of the Herd model above.

This model used several of Herd's built in features. Default definitions of relations like co, fr, rmw, as well as variants like external coherence  $(co_e)$  and external from-reads  $(fr_e)$ . Similarly, there are built in axiomatic constraints like empty and acyclic. Herd therefore not only provides a framework to build memory models, but also a set of assumptions about the structure of the model. These assumptions have proven in general to yield sensible models, notably ARM's

Figure 15: A fragment of an execution which would be forbidden by the atomicity axiom Herd SC model.

industrial model is a Herd model (Deacon and Alglave 2019), and C11 has a Herd model too. For some however, these assumptions prove to a be a little too restrictive. We will explore the NVIDIA PTX memory model in this thesis, which was originally expressed as a Herd model, but has since been re-expressed in a more custom Alloy-based approach.

#### 2.2.2 cppmem

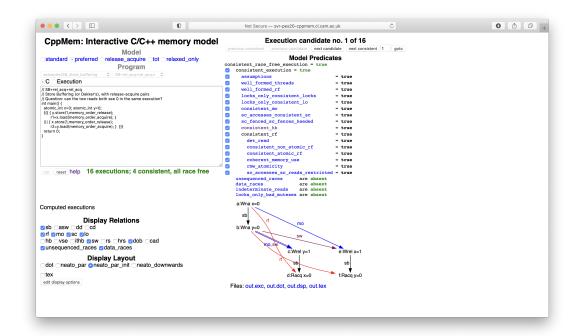

Alongside Mathemtizing C++ came a tool for automatically exploring the executions permitted by the proposed C++ memory model. The tool allows users to input tests in a C-like syntax and explore all the executions allowed by the model, as well as giving options to toggle some axioms of the memory model. Users can toggle certain axioms to see which axioms are giving the model strength against particular litmus tests. cppmem was essential in gaining acceptance of the new C++ model industrially, as it allowed the ISO C++ committee members to explore programs of interest and understand how the new memory model would affect them. Figure 16 shows a screenshot of cppmem running.

#### 2.2.3 Alloy

Alloy is a relational model checking tool which has been used in several memory model formalisations. Unlike Herd, Alloy is a general purpose tool – offering no direct help with construction of memory models. However, Alloy being general purpose allows a memory model author to express more bespoke patterns, which has proved especially useful for memory models that describe graphics systems. Axioms can be expressed as facts over the relations of the model, and a model checker can be used to generate consistent executions within these relations and axioms. Predicates can be expressed to attempt to search for programs which exhibit some weak behaviour, and the model checker can search for counter-examples. Alloy has been used to define

Figure 16: A screenshot of cppmem showing an allowed weak execution of the Store Buffering litmus test.

the PTX memory model (Lustig et al. 2017) (discussed in great detail in Chapter 3) and the Vulkan memory model (Khronos Group 2020), a cross-platform graphics API.

#### 2.2.4 memalloy

memalloy is a tool for finding minimal litmus tests which can distinguish two memory models (Wickerson et al. 2017). Memory models can be distinguished when a program P executed under memory model M has an outcome which is permitted, but forbidden when executed under a different memory model M'.

$$\operatorname{distinguishes}(P) \triangleq [\![P]\!]_M \neq [\![P]\!]_{M'}$$

memalloy existentially quantifies a P in a bounded universe to satisfy the constraint. The use of this is two-fold: it allows practitioners to demonstrate tests which can abstract complex axiomatic memory model details to communicate an intuition about the difference between models; and it enables the generation of new minimal litmus tests for automated testing. On a more meta-theoretic front, it provides a bounded means to test for strengthening or weakening of a model. When building a programming language model the language model should ideally

Figure 17: Load buffering litmus.  $r_1 = r_2 = 1$  is allowed in C++.

be weaker than the architecture model, or specific modifications (such as inserting a fence) to simply generated code must be made to preserve semantic meaning. Relaxed atomics in C/C++ are specified weakly enough that they may be compiled to native load and store instructions on x86 and ARM with no additional memory operations, as the programming language model of relaxed atomics is weaker than the hardware model of loads and stores<sup>3</sup>.

#### 2.3 The Thin-Air Problem

Unfortunately axiomatic memory models have been found to be inadequate for specifying programming languages (Batty et al. 2015). The interaction between compiler optimisations and apparent program dependencies breaks the ability of an axiomatic model to use the source program to accurately describe its behaviour. Axiomatic models are either too strong, and forbid optimisations which are important in practice, or too weak and permit nonsensical program behaviours which are not observable on real hardware and also prevent verification of program components. This problem is known as the Out of Thin Air (OOTA) Problem. To explore OOTA the sensible place to start is with the Load Buffering (LB) litmus test, listed in Figure 17.

In the LB litmus test data is loaded from a shared variable, and then stored to a different variable. This specific example has a constant store of 1 to x and y, which does not depend on the values read into registers  $\mathbf{r}_1$  or  $\mathbf{r}_2$ . In this instance, the execution where  $\mathbf{r}_1 = \mathbf{r}_2 = 1$  is allowed by ARM, and as such is also allowed in C++ – forbidding this execution in C++ would necessitate some compilation strategy which prevented the behaviour when targetting ARM, like emitting an additional fence in each thread.

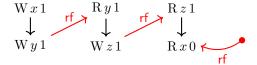

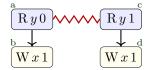

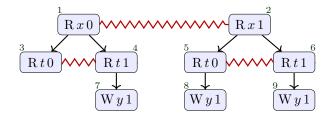

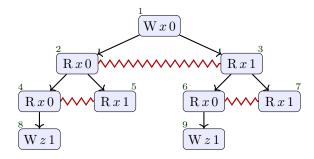

In Figure 18 the program has been modified to store values to x and y which are data-dependent on the value loaded into  $r_1$  and  $r_2$ . This program is known as LB+datas, and the outcome where  $r_1 = r_2 = 42$  would be quite unreasonable: to store 42 to x we must first have loaded 42 from y; to store 42 to y we must have first loaded 42 from x. There is no interleaving or re-ordering of instructions which could yield this result, the calculation of the value for 42 is

<sup>&</sup>lt;sup>3</sup>There is a caveat for mixed-sized atomics which are poorly specified for hardware models (Flur et al. 2017)

Figure 18: Load buffering litmus test with data dependencies. The thin-air behaviour would be observing that  $r_1 = r_2 = 42$ .

self-referential. Informally, an execution where this outcome is observed would require some cycle in dependency (dep) and rf. We might consider, then, a rule which forbids cycles in (dep  $\cup$  rf). Next, consider a small variation of this test, where the data dependencies are replaced with control dependencies.

Initially:

$$\mathbf{x} := 0$$

;  $\mathbf{y} := 0$ ;

$$\mathbf{r}_1 := \mathbf{x};$$

$$\mathbf{if}(\mathbf{r}_1 = 1)\{\mathbf{y} := 1\}$$

$$\mathbf{r}_2 := \mathbf{y};$$

$$\mathbf{if}(\mathbf{r}_2 = 1)\{\mathbf{x} := 1\}$$

$$\mathbf{r}_3 := \mathbf{y};$$

$$\mathbf{r}_4 := \mathbf{y};$$

$$\mathbf{r}_5 := \mathbf{y};$$

$$\mathbf{r}_7 := \mathbf{r}_7 := \mathbf{r$$

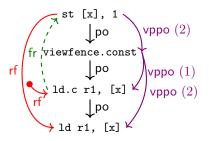

The test starts with x and y initialised to 0, then two threads concurrently read and conditionally write 1 back to their respective variables. The outcome  $\mathbf{r}_1 = \mathbf{r}_2 = 1$  (1/1) is unintuitive, and it cannot result from SC: there is no interleaving that agrees with the program order and places the writes of 1 before the reads for both x and y.

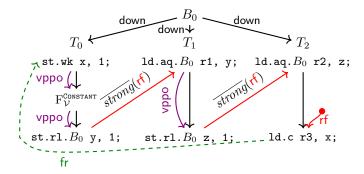

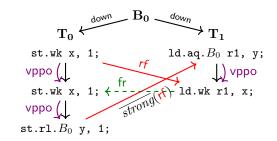

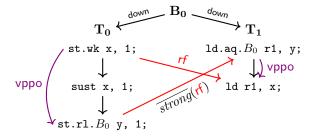

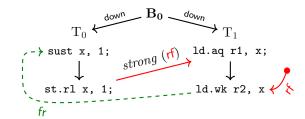

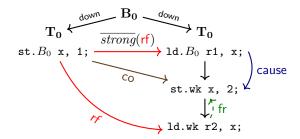

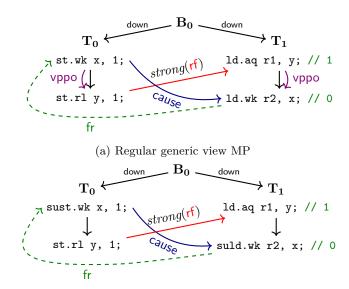

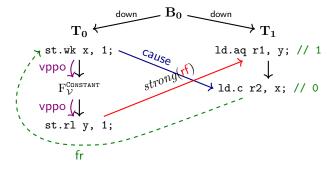

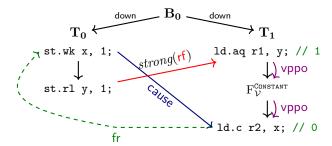

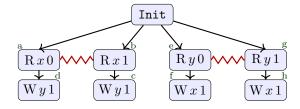

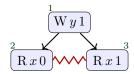

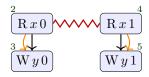

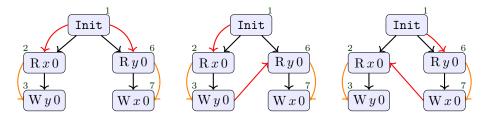

In an axiomatic specification, the outcome specified by the test corresponds to the execution graph shown alongside the source code. The axiom  $\operatorname{acyclic}(\mathsf{po} \cup \mathsf{rf})$  forbids the outcome 1/1 as the corresponding execution contains a cycle. Indeed the SC, x86, Power and ARM memory models each include a variant of this axiom, all forbidding 1/1, whereas the C++ standard omits it (Batty et al. 2011) and allows 1/1.

To better understand why C++ does not forbid the cycle in  $po \cup rf$ , we will look at a further example which illustrates why axiomatic models are not well suited for programming language memory models.

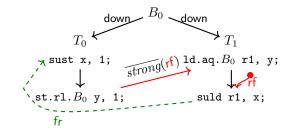

Axiomatic specifications do not fit optimised languages. Languages like C++ and Java perform dependency-removing optimisations that complicate their memory specifications. For example, the second thread of the LB+false-dep test (presented below) can be optimised using common sub-expression elimination to reg2 := y; x := 1. This kind of control dependency is said to be a *false dependency*, as the outcome of the if-statement does not rely on the value read in  $r_2$ : it will write x := 1 in the true and false branches. In the unoptimised code, the control dependency would have prevented code motion. However in the compiled code where the compiler optimises this control flow away, ARM and Power allow load/store reordered where there is no dependency between the operations, so the relaxed 1/1 outcome is allowed.

The memory model of the C++ standard (ISO/IEC 2010) is flawed because its axiomatic model cannot draw a distinction between the executions leading to outcome 1/1 in LB+ctrl and LB+false-dep. To see that the dependency is false, one must consider more than one execution path, but axiomatic models judge single executions only (Batty et al. 2015). This is illustrated below, where the 1/1 executions of LB+false-dep and LB+ctrl are drawn. The executions are identical with no distinguishing features, as all control flow choices are elided once programs are reduced to executions.